#### UNIVERSIDAD POLITÉCNICA DE MADRID

## Escuela Universitaria de Ingeniería Técnica de Telecomunicación

Proyecto Fin de Carrera

# Implementación de un sistema multicanal de medida de temperatura con termopares

Autora: Silvia Callejas González Tutor: Mariano Ruiz González

Madrid, 2013

If you need something to walk forward, just put your headphones in and press play.

## Índice

| Ín | dice    |                                                                   | v    |

|----|---------|-------------------------------------------------------------------|------|

| Ín | dice d  | e figuras                                                         | ix   |

| Ín | dice d  | e tablas                                                          | xi   |

| Α  | gradec  | imientos                                                          | xiii |

| R  | esume   | n                                                                 | xv   |

| A  | bstract |                                                                   | xvii |

| 1  | Intr    | oducción                                                          | 1    |

| 2  | Req     | uisitos del sistema                                               | 3    |

|    | 2.1     | Introducción                                                      | 3    |

|    | 2.2     | Especificaciones del diseño                                       | 4    |

|    | 2.3     | Objetivos de aprendizaje                                          | 5    |

|    | 2.1     | Entorno de trabajo                                                | 6    |

| 3  | Des     | cripción del sensor de temperatura                                | 9    |

|    | 3.1     | Introducción                                                      | 9    |

|    | 3.2     | Termoelectricidad                                                 | 10   |

|    | 3.3     | Termopares. El efecto Seebeck                                     | 10   |

|    | 3.4     | Tipos de Termopares                                               | 13   |

|    | 3.5     | Sensor Utilizado: Tipo J                                          | 16   |

| 4  | Des     | cripción del conversor                                            | 19   |

|    | 4.1     | Introducción                                                      | 19   |

|    | 4.2     | Conversor de Termopar a Digital con Compensación de la Unión Fría | 20   |

|    | 4.2.    | l Descripción Hardware                                            | 20   |

|    | 4.2.2   | 2 Descripción Software                                            | 23   |

| 5  | Sist    | ema de control y procesado: FPGA                                  | 27   |

|    | 5.1     | Introducción                                                      | 27   |

|    | 5.2     | FPGA                                                              | 28   |

|    | 5.3     | Kit de desarrollo                                                 | 29   |

|    | 5.4     | Diagrama de bloques                                               | 30   |

| 6  | Arq     | uitectura del sistema completo                                    | 33   |

|    | 6.1     | Introducción                                                      | 33   |

|    | 6.2     | Visión general del sistema completo                               | 34   |

| 7 Blo | oque I: Conversión                                             | 37 |

|-------|----------------------------------------------------------------|----|

| 7.1   | Introducción                                                   | 37 |

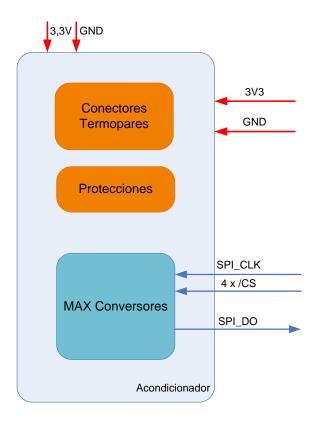

| 7.2   | Diagrama de bloques                                            | 38 |

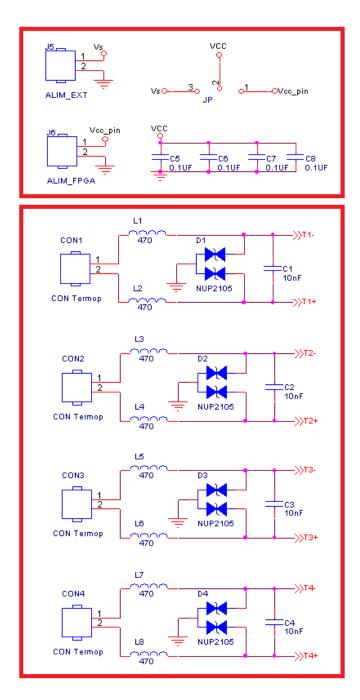

| 7.3   | Esquemático                                                    | 39 |

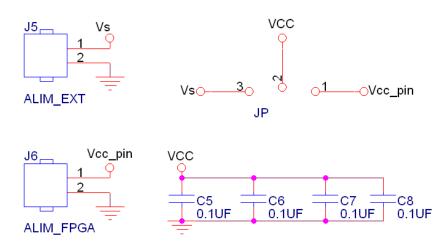

| 7.3   | .1 Alimentación                                                | 39 |

| 7.3   | .2 Conectores de termopar y protecciones                       | 39 |

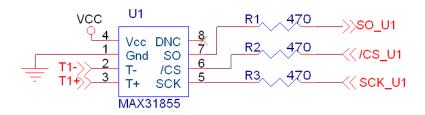

| 7.3   | .3 Circuito de conexión del MAX31855                           | 40 |

| 7.4   | Diseño                                                         | 41 |

| 7.4   | .1 Diseño PCB                                                  | 41 |

| 7.4   | .1 Fabricación del PCB                                         | 42 |

| 7.4   | .2 Montaje de los componentes                                  | 43 |

| 7.4   | .3 Costes                                                      | 45 |

| 8 Blo | oque II: Procesado digital                                     | 47 |

| 8.1   | Introducción                                                   | 47 |

| 8.2   | Periféricos utilizados                                         | 48 |

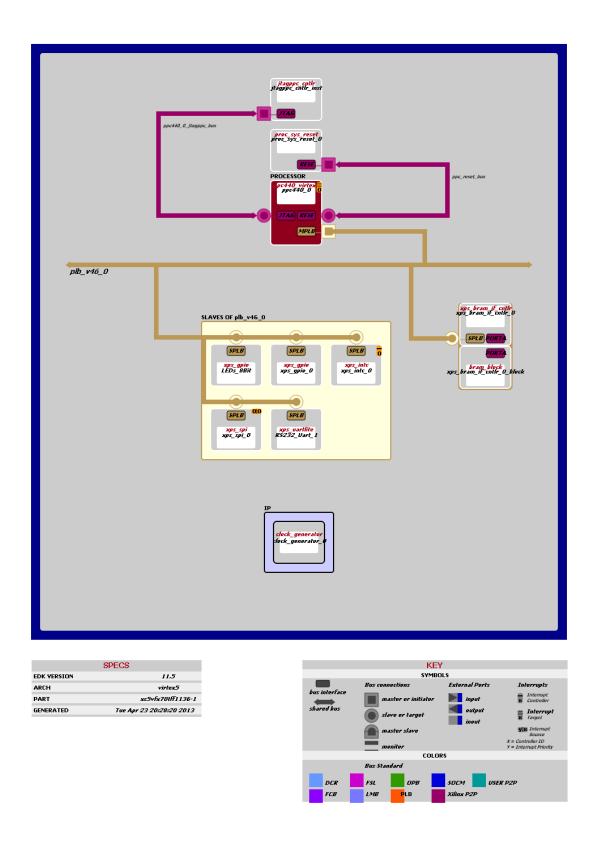

| 8.3   | Configuración de la FPGA: XPS                                  | 48 |

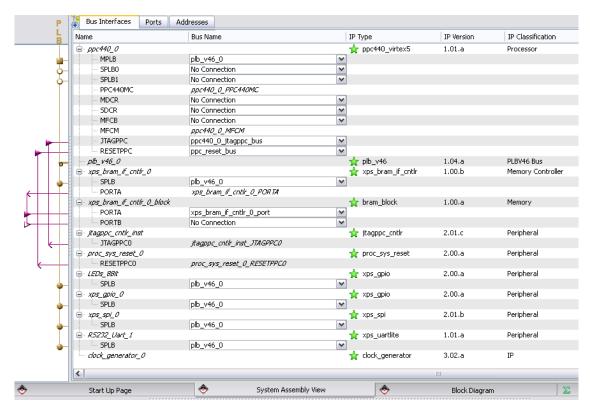

| 8.3   | .1 Bloques VHDL y drivers implementados en la plataforma XPS   | 49 |

| 8.3   | .1 Restricciones del sistema y pines de entrada salida         | 53 |

| 8.4   | Programación del procesador: SDK                               | 55 |

| 9 Blo | oque III: Procesado de datos en el PC                          | 59 |

| 9.1   | Introducción                                                   | 59 |

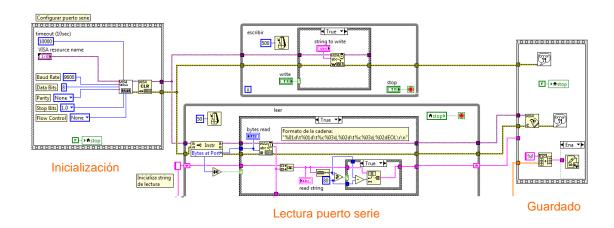

| 9.2   | Captura y procesado de la trama mediante LabVIEW               | 60 |

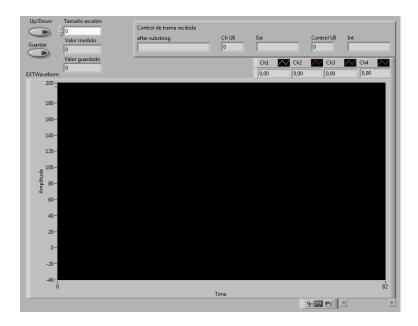

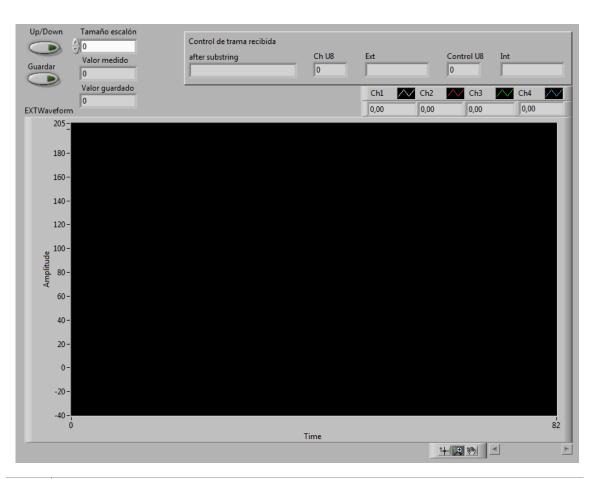

| 9.3   | Interfaz de usuario LabVIEW                                    | 65 |

| 9.3   | .1 Interfaz de usuario para visualización de medidas           | 65 |

| 9.3   | .2 Interfaz de usuario para visualización y captura de medidas | 66 |

| 10 I  | Proceso de calibración                                         | 67 |

| 10.1  | Introducción                                                   | 67 |

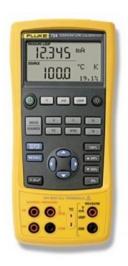

| 10.2  | Calibrador del sistema                                         | 68 |

| 10.3  | Cálculos de ajuste y calibración mediante Excel                | 69 |

| Pri   | mer método de calibración                                      | 70 |

| Seg   | gundo método de calibración                                    | 73 |

| 10.4  | Verificación de los cálculos de calibración                    | 75 |

| 11 (  | Conclusiones y posibles mejoras                                | 77 |

| 11.1  | Conclusiones                                                   | 77 |

| 11.2     | Posibles mejoras                                                       | 78  |

|----------|------------------------------------------------------------------------|-----|

| 12 A     | Apéndices                                                              | 79  |

| 12.1     | Esquemático completo del Bloque I                                      | 81  |

| 12.2     | Fotolitos para la fabricación de la placa acondicionadora del Bloque I | 82  |

| 12.3     | Lista de componentes necesarios. MPL (Master Part List)                | 83  |

| 12.4     | IPCores de XPS                                                         | 85  |

| 12.5     | Diagrama de bloques de XPS                                             | 86  |

| 12.6     | Restricciones del usuario UCF (User Constraints File)                  | 87  |

| 12.7     | Código de programa en C del PowerPC440                                 | 88  |

| 12.8     | Código del archivo MHS                                                 | 96  |

| 12.9     | Código del archivo MSS                                                 | 99  |

| 12.10    | Código del archivo *.UCF                                               | 101 |

| 12.11    | Código LabVIEW                                                         | 102 |

| Par      | nel frontal básico de usuario                                          | 104 |

| Par      | nel frontal de calibración                                             | 104 |

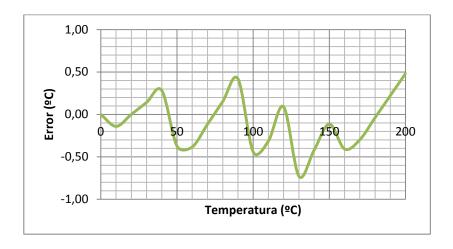

| 12.12    | Cálculos y gráficas en Excel de los cuatro canales                     | 105 |

| Caı      | nal 1                                                                  | 105 |

| Caı      | nal 2                                                                  | 106 |

| Caı      | nal3                                                                   | 107 |

| Caı      | nal4                                                                   | 108 |

| Bibliogr | afía                                                                   | 109 |

## Índice de figuras

| Figura 1. Diagrama del desarrollo.                                                | 3  |

|-----------------------------------------------------------------------------------|----|

| Figura 2. Diagrama de bloques del sistema completo.                               | 5  |

| Figura 3. Termopar tipo J.                                                        |    |

| Figura 4. Efecto Seebeck: Al aplicar calor a una unión de las uniones de dos      |    |

| materiales diferentes, se crea una diferencia de tensión proporcional a           |    |

| la temperatura aplicada                                                           | 10 |

| Figura 5. Unión fría creada al conectar un instrumento de media en los bornes del |    |

| termopar, con ello se crean tensiones parásitas que deben ser                     |    |

| compensadas                                                                       | 12 |

| Figura 6. Modelo de compensación de la unión fría mediante región isotérmica.     |    |

| Se crean dos nuevas uniones de las mismas características (J2 y J4) de            |    |

| este modo se anulan las tensiones parásitas (VJ2 y VJ4). La                       |    |

| compensación de la tensión parásita V <sub>J</sub> 3 se debe hacer mediante       |    |

| software o hardware                                                               | 12 |

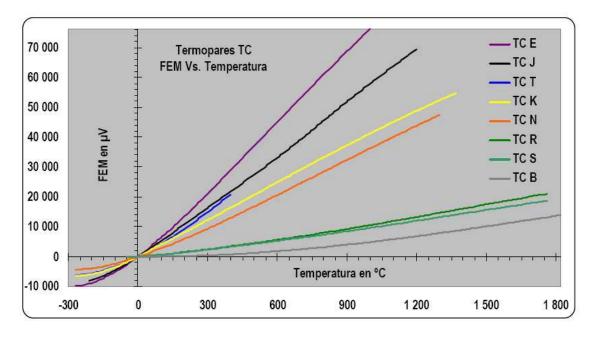

| Figura 7. Tensión de termopar frente a temperatura según los diferentes tipos de  |    |

| termopares                                                                        | 16 |

| Figura 8. Encapsulado MAX31855                                                    | 19 |

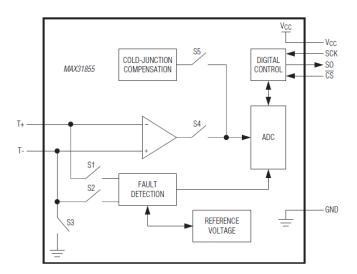

| Figura 9. Diagrama de bloques. MAX31855, incluye un amplificador operacional,     |    |

| detección del estado de la conexión del termopar y un bloque especial             |    |

| para la compensación de la unión fría así como un ADC para hacer la               |    |

| conversión de termopar adigital                                                   | 20 |

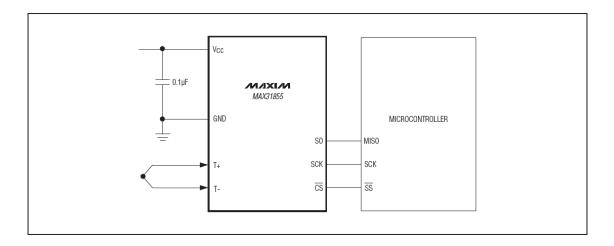

| Figura 10. Circuito de aplicación típico del MAX31855, a la entrada se conecta el |    |

| termopar, la comunicación SPI se gestionará en este caso con el                   |    |

| procesador de la FPGA                                                             | 21 |

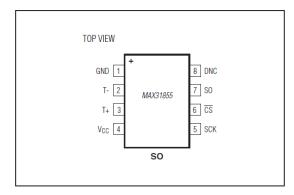

| Figura 11. Pinout del MAX31855. Encapsulado tipo SOP de 8 pines                   | 23 |

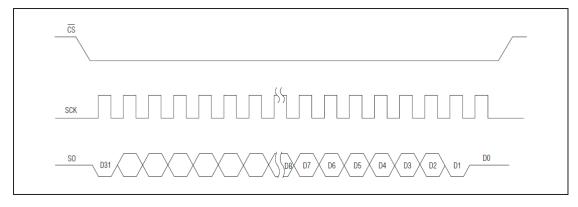

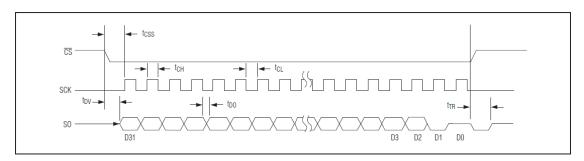

| Figura 12. Diagrama del protocolo de la comunicación SPI.                         | 23 |

| Figura 13. Diagrama de tiempos de la comunicación SPI.                            | 24 |

| Figura 14. Vista simplificada de una FPGA.                                        |    |

| Figura 15. Esquema de la arquitectura interna de una FPGA.                        |    |

| Figura 16. Placa de desarrollo Virtex-5 ML507.                                    | 29 |

| Figura 17. Diagrama de bloques de la plataforma de evaluación FPGA Virtex-5       |    |

| ML507                                                                             |    |

| Figura 18. Diagrama de bloques global                                             | 33 |

| Figura 19. Sistema completo.                                                      |    |

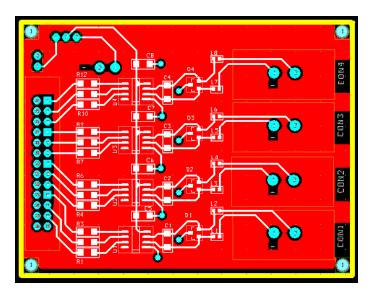

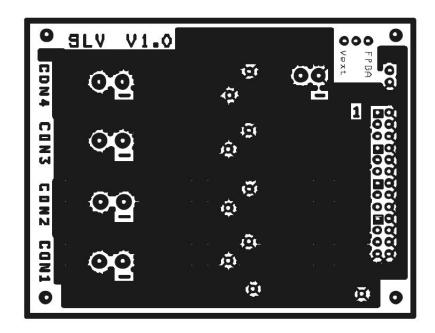

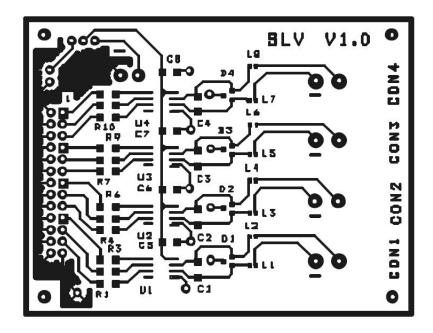

| Figura 20. Placa acondicionadora de señal (Bottom)                                | 37 |

| Figura 21. Bloque de conversión.                                                  | 38 |

| Figura 22. Conectores de alimentación, jumper de selección y condensadores de     |    |

| desacoplo para los circuitos integrados                                           |    |

| Figura 23. Conector de termopar y circuito de protección                          |    |

| Figura 24. Circuito de conexión del MAX31855.                                     |    |

| Figura 25. Diseño PCB en OrCAD Layout                                             | 41 |

| Figura 26 | Insoladora donde se colocará la placa con el fotolito                 | 42 |

|-----------|-----------------------------------------------------------------------|----|

| Figura 27 | . Equipo de revelado y atacado con calentadores para los líquidos y   |    |

|           | generador de burbujas que aceleran el proceso de fabricación          | 43 |

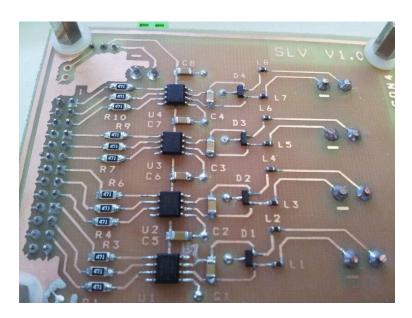

| Figura 28 | . Placa acondicionadora finalizada.Detalle soldadura                  | 44 |

| Figura 29 | . Placa acondicionadora finalizada                                    | 44 |

| Figura 30 | . FPGA Virtex 5                                                       | 47 |

| Figura 31 | Diagrama de bloques implementados en la plataforma de desarrollo      |    |

| Ü         | Virtex-5                                                              | 48 |

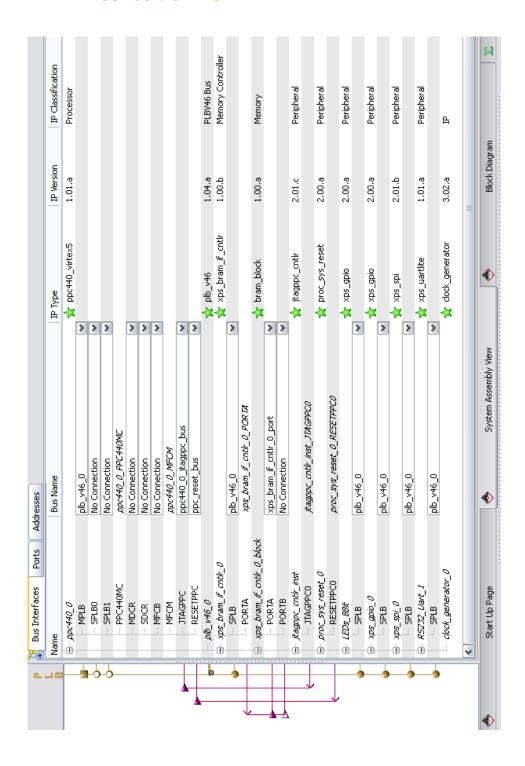

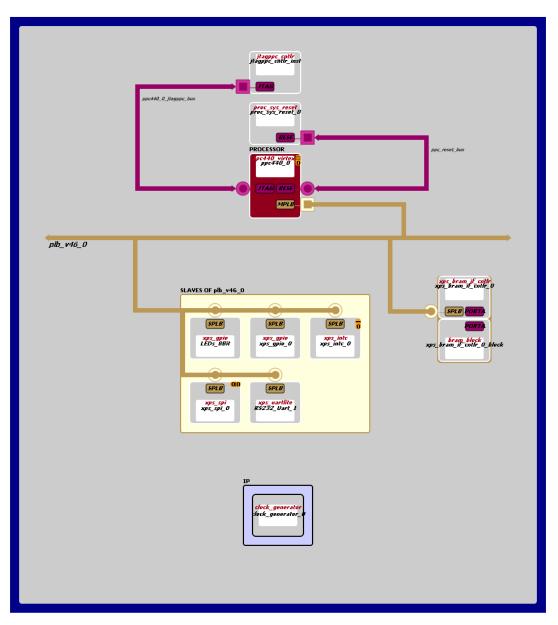

| Figura 32 | . Bus de interfaces implemntadas en la plataforma de desarrollo XPS   | 50 |

| Figura 33 | Diagrama de bloques de los IPCores implementados mediante la          |    |

| _         | plataforma de desarrollo XPS                                          | 51 |

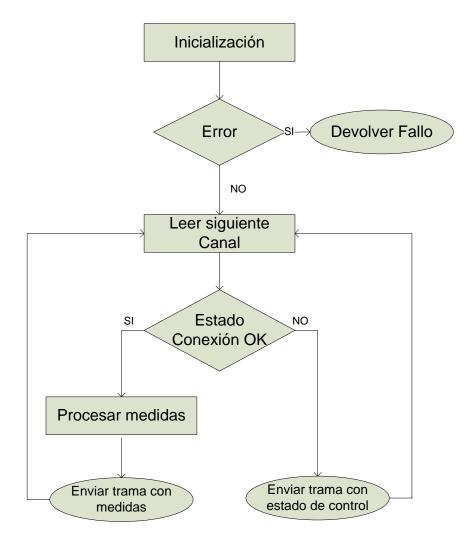

| Figura 34 | Diagrama de flujo del programa principal del procesador PowerPC440    | 56 |

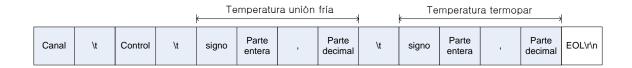

| Figura 35 | Trama de temperaturas para comunicación RS-232                        | 57 |

| Figura 36 | . Logo del programa LabVIEW de National Instruments                   | 59 |

| _         | . Código LabVIEW para lectura escritura de puerto serie               |    |

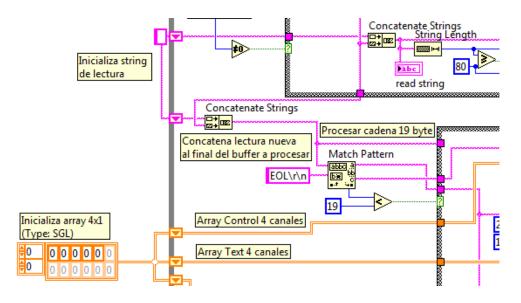

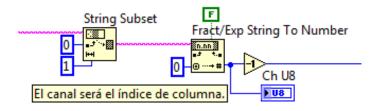

| Figura 38 | . Inicio del procesado de la trama leída                              | 61 |

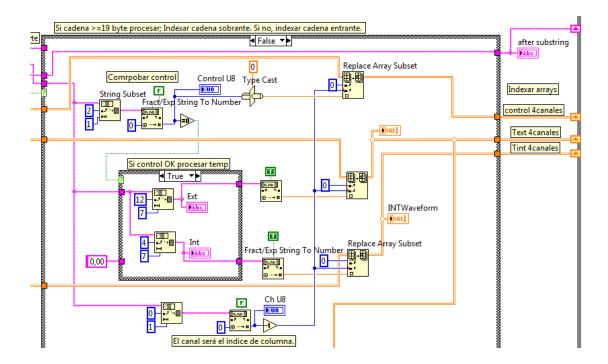

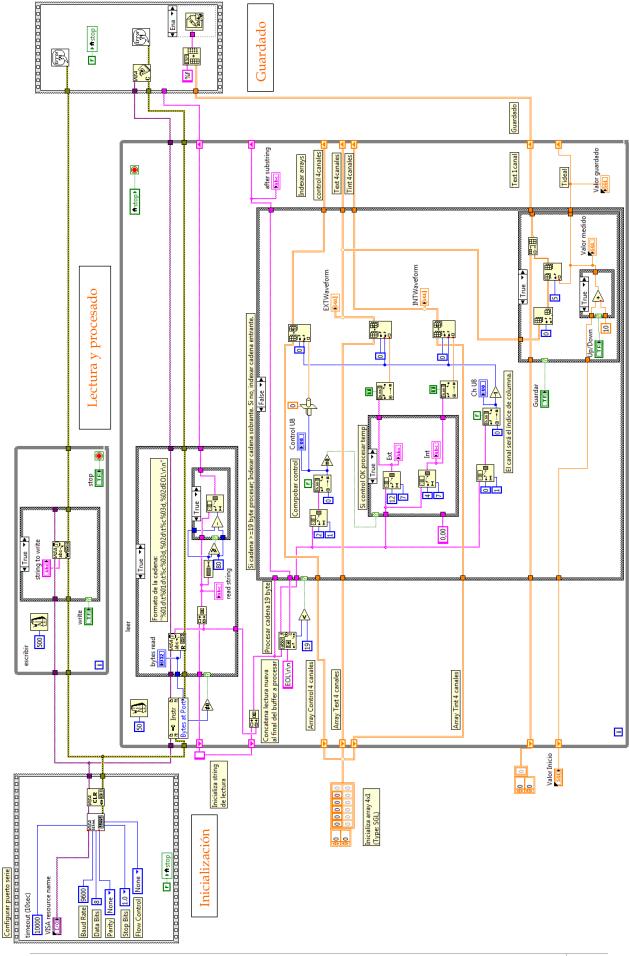

| Figura 39 | . Procesado de la trama, código completo                              | 62 |

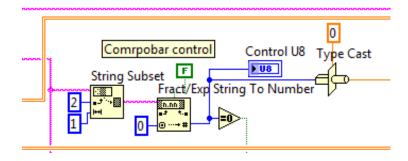

|           | . Procesado de la trama, comprobación del estado de la conexión. Byte |    |

| <u> </u>  | de control                                                            | 63 |

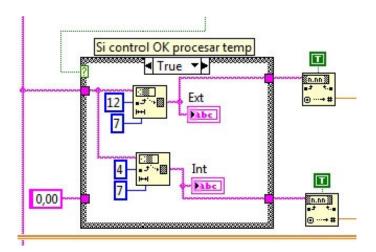

| Figura 41 | . Procesado de la trama. Procesado de temperaturas con valor decimal  | 63 |

| Figura 42 | . Procesado de trama de medida. Índice de canal medido                | 64 |

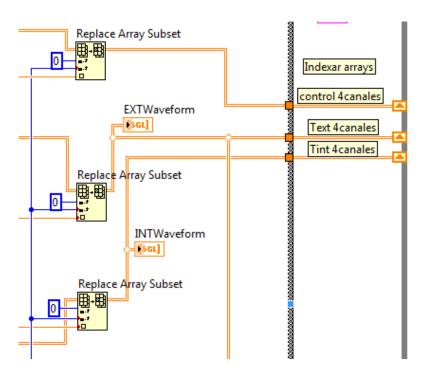

| Figura 43 | . Procesado de trama de medidas. Guardado de datos en array           | 64 |

| Figura 44 | . Interfaz gráfica de usuario en LabVIEW                              | 65 |

| Figura 45 | . Interfaz gráfica de usuario en LabVIEW                              | 66 |

|           | . Calibrador FLUKE 725                                                |    |

| Figura 47 | . Sistema completo con el calibrador utilizado                        | 68 |

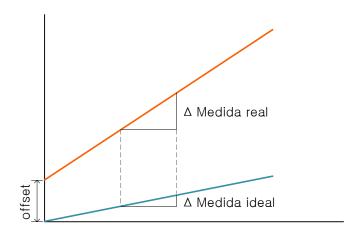

| Figura 48 | . Representación gráfica de los errores de genancia y offset          | 69 |

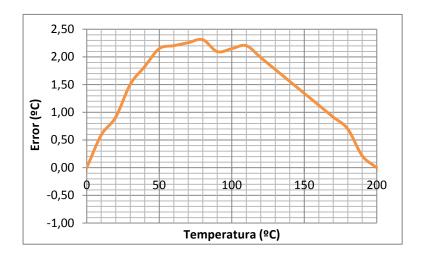

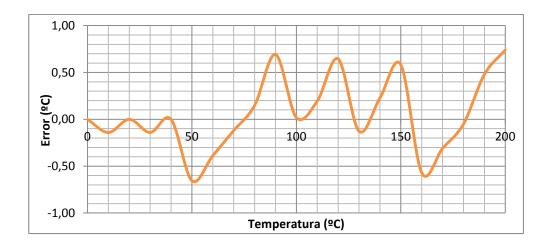

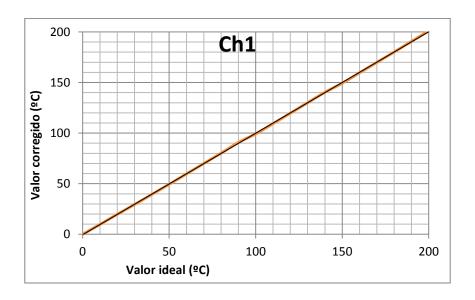

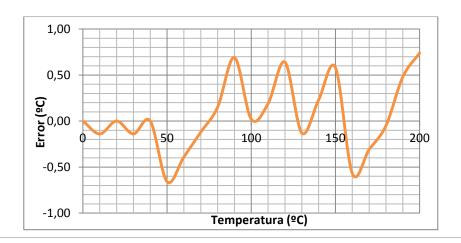

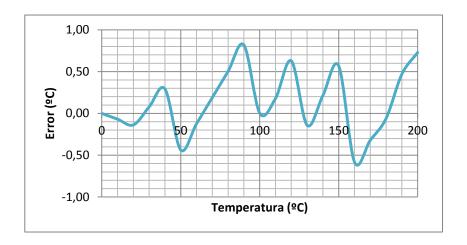

| O         | . Error de medida tras la calibración por el primer método            |    |

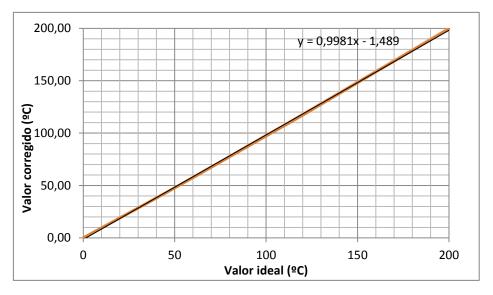

| _         | . Comparación del valor medido respecto al ideal con el primer método |    |

| O         | de calibración.                                                       | 72 |

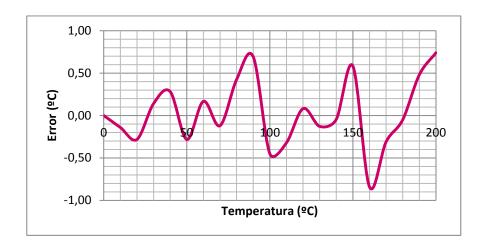

| Figura 51 | . Error de medida tras la calibración por el segundo método           |    |

| 0         | . Comparación de la medida real frente a la ideal con el segundo      |    |

| Ü         | método de calibración.                                                | 74 |

## Índice de tablas

| Tabla 1. Comparativa de los tipos de de termopares más comunes según material     |      |

|-----------------------------------------------------------------------------------|------|

| y rango de temperatura                                                            | 15   |

| Tabla 2. Coeficientes para la calibración de termopar tipo J en función del rango |      |

| de temperatura                                                                    | 17   |

| Tabla 3. Condiciones de trabajo del MAX31855 recomendados por el fabricante       | . 21 |

| Tabla 4. Características térmicas y tiempos de conversión del MAX31855 en su      |      |

| versión para termopar tipo J.                                                     | 22   |

| Tabla 5. Características de los tiempos en la comunicación SPI                    | 24   |

| Tabla 6. Descripción del Mapa de Memoria. Indica la posición de los bits y la     |      |

| información de la trama                                                           | 25   |

| Tabla 7. Formato de la temperatura en la trama de comunicación serie. Izquierda:  |      |

| temperatura del termopar, derecha: temperatura de la unión fría                   | 25   |

| Tabla 8. Costes de fabricación del PCB.                                           | 45   |

| Tabla 9. Resumen de recursos utilizados en la FPGA                                | 52   |

| Tabla 10. Localización de los LEDs en la FPGA                                     | 53   |

| Tabla 11. Localización del conector de expansión J6 en la FPGA                    | 54   |

| Tabla 12. Cálculos del primer método de calibración realizados con Excel          | 71   |

| Tabla 13. Cálculos del segundo método de calibración realizados con Excel         | 73   |

|                                                                                   |      |

#### **Agradecimientos**

Qué mejor broche para cerrar este ciclo que agradecer a todos los que han estado conmigo en los últimos años de estudio, tanto en los libre acceso y en la biblioteca estudiando y terminando prácticas hasta las tantas, como en los ratos libres de descanso merecido para desconectar.

Gracias también en especial a Mariano, mi tutor, por ayudarme y orientarme en todo el desarrollo, y por preocuparse siempre de que sus alumnos estemos bien y hagamos nuestro trabajo aprendiendo el máximo posible.

Por supuesto, y rozando la originalidad, quiero agradecer a mis padres todo lo que han apostado por mí, y los ánimos y los "acuéstate que ya es tarde, mañana sigues" y un largo etcétera. Gracias por estar ahí, por toda vuestra ayuda y aguantar el trabajo que os damos.

Mi hermana se merece un apartado especial en exclusiva en esta página, Rosi, tú siempre me lees y sabes antes que nadie lo que me pasa, gracias por tus consejos y por todos esos pasos que me has ahorrado cuando tú te los has tenido que trabajar.

Muchas gracias PANDA por estar ahí siempre, pase lo que pase y sea cuando sea. Nos fundamos hace casi diez años y ya somos diez, seguiremos sumando y creciendo, viajando y riendo...y jugando, por supuesto.

Gracias también a toda la gente de AETEL, vosotros sois los que más me habéis visto estos meses siempre acompañada del portátil y sin otro tema de conversación casi que no fuese sobre el proyecto. Os meto caña pero sabéis que es desde el cariño.

¡¡Mangueros!! Los veranos se hacen más cortos, pero aprovechables al 100%, mínimo una semana al año no se perdona, esperemos que pueda ser más.

Néstor, gracias por hacerme este camino más fácil. Te debo una, o dos, o mil. Rober, tú has estado ahí desde el primer día, y por muy lejos que te vayas no te libras de mí, ya lo sabes. Barras, mucho ánimo que esto acaba. Alberto y Guti, esos libres accesos marcarán época. Extre, ¿me traerás esas cerezas como premio por haber llegado hasta aquí? Tania, gracias por tus minidetallazos que alegran el día y por recordarme que el túnel acaba sin que te des cuenta de que has llegado al final. Jana, mi compi en el extranjero, al final presentamos el mismo año ¿dónde nos vamos para celebrarlo?

Al gañán de turno le quiero dar las gracias por aguantarme y por todo lo que me ha ayudado, aunque diga que no. Richi, gracias por las risas cuando no había manera de encontrarlas.

Quiero agradecer a Juanjo, Javi, Carlos, Luis y Chechu por la gran oportunidad y toda la ayuda que me han dado a lo largo de estos meses.

#### Resumen

Este proyecto fin de carrera tiene como finalidad el diseño e implementación de un sistema multicanal de medida de temperaturas con termopares con procesado digital.

Se ha realizado un prototipo de cuatro canales con conexión de termopar, que es el tipo de sensor utilizado para realizar dichas medidas. La tensión generada por el termopar es procesada mediante un conversor de termopar a digital con salida en interfaz modo serie o SPI (Serial Peripheral Interface). El control de dicha comunicación se realiza por medio de un Array de Puertas Lógicas Programables o FPGA (Field Programmable Gate Array), en concreto se ha utilizado una plataforma de desarrollo modelo Virtex-5 de la empresa Xilinx. Esta tarjeta se ha programado también para el procesado software y la posterior comunicación serie con el PC, el cual consta de una interfaz de usuario donde se muestran los resultados de las medidas en tiempo real.

El proyecto ha sido desarrollado en colaboración con una empresa privada dedicada principalmente al diseño electrónico. La finalidad de este prototipo es el estudio de una actualización del bloque de medida para el control de las curvas de temperatura de un equipo de reparación aeronáutica.

En esta memoria se describe el proceso realizado para el desarrollo del prototipo, incluye la presentación de los estudios realizados y la información necesaria para llevar a cabo el diseño, la fabricación y la programación de los diferentes bloques que componen el sistema.

#### **Abstract**

The aim of this project is to implement a multichannel temperature measurement system with digital processing, using thermocouples.

A four-channel prototype with thermocouple connection has been built. The thermocouple voltage is converted to digital line using a Thermocouple-to-Digital Converter with a Serial Perpheral Interface (SPI) output. The master which controls this communication is embedded in a Field Programmable Gate Array (FPGA), specifically the Xilinx Virtex-5 model. This FPGA also has the code for software temperature processing and the prototype to PC serial communication embedded. The PC user interface displays the measurement results in real time.

This project has been developed at a private electronics design company. The company wants to study an update to change the analogue temperature controller equipment to a digital one. So this prototype studies a digital version of the temperature measurement block.

The processes accomplished for the prototype development are detailed in the next pages of this document. It includes the studies and information needed to develop the design, manufacturing process and programming of the blocks which integrate with the global system.

#### 1 Introducción

Este documento está dividido en 12 capítulos en los cuales se explica el estudio, desarrollo, diseño e implementación del proyecto realizado. Se detallan también los elementos empleados en cada bloque tanto sensores, conversores, sistemas digitales, programas utilizados, como los estudios realizados y descripciones necesarias para comprender el funcionamiento y manejo del prototipo. A continuación se presenta un breve resumen del contenido de los siguientes capítulos.

Capítulo 2. Requisitos del sistema. Se presentan las especificaciones iniciales, así como las especificaciones propuestas para el diseño del sistema. Se incluyen también los objetivos de aprendizaje, y el entorno de trabajo con las herramientas necesarias para llevar a cabo la fabricación e implementación del prototipo.

Capítulo 3. Descripción del sensor de temperatura. Se presenta una breve introducción a la termoelectricidad en lo referente a termopares. También se incluye una descripción de los tipos de termopares que se encuentran en el mercado, y se define el tipo de termopar utilizado en este proyecto.

Capítulo 4. Descripción del conversor. En este capítulo se hace un estudio de la hoja de características del conversor empleado, el MAX 31855 del fabricante Maxim, mostrando desde el diagrama de bloques interno hasta el formato de la trama de salida en su comunicación de interfaz serie (SPI), pasando por los tiempos de comunicación, los valores de tensión de alimentación, frecuencia de trabajo y el pinout del componente.

Capítulo 5. Sistema de control y procesado: FPGA. Aquí se explica brevemente cómo es una FPGA internamente, sus inicios y evolución. También se presenta el kit

de desarrollo Virtex-5, que es el que se emplea en este proyecto, junto con las herramientas de desarrollo necesarias.

Capítulo 6. Arquitectura del sistema completo. Para facilitar la comprensión de la descripción de los bloques que componen este proyecto, en este capítulo se muestra el sistema completo diferenciando los bloques por los que está compuesto e indicando el tipo de comunicación utilizado entre cada uno de ellos.

Capítulo 7. Bloque I: Conversión. Presentación del esquemático de la placa fabricada, incluyendo los componentes empleados y el funcionamiento de la placa. Así como una descripción del diseño mediante la herramienta OrCAD y fabricación de la misma por método manual en laboratorio.

Capítulo 8. Bloque II: Procesado digital. Se describen los periféricos de la tarjeta Virtex-5 que se emplean en este proyecto así como su configuración, la cual se realiza mediante la herramienta de desarrollo XPS (Xilinx Platform Studio), junto con la descripción de cada periférico en lenguaje hardware VHDL. También se incluye en este capítulo la programación del procesador embebido en la FPGA, mediante la herramienta de desarrollo software SDK (Software Development Kit)

Capítulo 9. Software: Procesado de medidas y comunicación con el PC. Aquí se incluye por una parte el software de procesado de medidas que ejecutará el microcontrolador Power PC 440, y por otra la aplicación diseñada en LabVIEW para el control de la comunicación mediante puerto serie y visualización de resultados en el PC.

Capítulo 10. Proceso de calibración. En este capítulo se describe el método utilizado para el ajuste de las medidas, incluyendo las ecuaciones que se deben aplicar a dichas medidas. Del mismo modo, se presentan los resultados obtenidos así como el proceso de verificación de los mismos.

Capítulo 11. Conclusiones y posibles mejoras. Aquí se detallan las conclusiones finales tras el proceso de diseño y desarrollo del proyecto completo. También se detallan posibles mejoras para versiones futuras del sistema.

Capítulo 12. Apéndices. Recoge los documentos necesarios para fabricar la placa de conversión, el código ejecutado por el procesador y los bloques de la aplicación software para el PC, así como las hojas de cálculo de calibración.

#### 2 Requisitos del sistema

#### 2.1 Introducción

Figura 1. Diagrama del desarrollo.

En este proyecto se desarrolla el prototipo de un sistema de medida de temperaturas de cuatro canales. El diseño está orientado a formar parte del control de temperatura de un equipo industrial de reparación aeronáutica.

Con este diseño se pretende sustituir el sistema analógico actual, por uno digital de modo que se consigue un gran ahorro en tamaño y componentes empleados. Los sistemas digitales tienen muchas ventajas frente a los analógicos, por ejemplo, se consigue mayor inmunidad al ruido en las transmisiones evitando así las distorsiones que se producen en los sistemas analógicos; requieren menos ajustes hardware puesto que la mayoría se hacen mediante software, lo que se traduce también en un menor coste en actualizaciones; la integración de sistemas resulta mucho más sencilla y más fácil de estandarizar. Como resultado, el sistema digital es un sistema mucho más flexible con un menor coste hardware.

En este capítulo se muestran las especificaciones del sistema, tanto los requisitos iniciales como la especificación final propuesta para el diseño. Del mismo modo, se presentan los objetivos de aprendizaje y el entorno de desarrollo con las herramientas necesarias para implementar el prototipo, tanto la parte hardware como la parte software, y las herramientas necesarias para realizar las pruebas de funcionamiento del sistema. Las diferentes fases del proceso de desarrollo del sistema se pueden ver en el diagrama de la figura 1.

#### 2.2 Especificaciones del diseño

El prototipo a desarrollar debe cumplir unas especificaciones determinadas. Las especificaciones básicas requieren que el prototipo conste de cuatro canales de medida con conexión de termopar tipo J, y un error que no supere ±1°C. El procesado de las medidas se realizará de forma digital, mediante una placa de Array de Puertas Lógicas Programable FPGA (del inglés Field Programmable Gate Array). Concretamente se dispone del modelo Virtex-5 en su versión ML507 del fabricante Xilinx. El motivo del uso de esta placa es el interés en el aprendizaje de la configuración y programación de la misma, para en un futuro poder desarrollar aplicaciones más complejas en sistemas embebidos.

Tras estudiar las especificaciones básicas, se ha realizado una propuesta de especificación más detallada, en la que se añade el tipo de conversión y comunicaciones que se van a realizar.

- El prototipo constará de cuatro canales de medida.

- El sensor de medida utilizado será termopar Tipo J.

- La conversión de termopar a digital se realizará con el MAX31855 del fabricante Maxim.

- El procesado y las comunicaciones serán gestionadas mediante la FPGA modelo Virtex-5 FXT FPGA ML507 del fabricante Xilinx.

- La interfaz de usuario y la programación de los diferentes elementos se realizarán en un PC con sistema operativo Windows en la versión necesaria para cada aplicación.

A continuación, en la figura 2, se puede ver el diagrama de los bloques que componen el prototipo desarrollado. El diseño consta de dos bloques hardware diferenciados. El primero se encarga de la conversión a trama digital de las temperaturas medidas, las cuales llegan al segundo bloque mediante una comunicación serie, desde este bloque se controlan las comunicaciones y se procesan dichas medidas, una vez procesadas se envían mediante puerto serie al PC. Este, a su vez, es el último bloque del sistema, el bloque software donde se implementa la interfaz de usuario para la visualización de las medidas en tiempo real y el calibrado del sistema.

El funcionamiento de los diferentes bloques se explica en los siguientes capítulos, así como los elementos empleados y los tipos de comunicación que se realizan entre cada módulo.

Figura 2. Diagrama de bloques del sistema completo.

#### 2.3 Objetivos de aprendizaje

El diseño de este proyecto aúna conocimientos de diversos ámbitos de la electrónica. Para la parte de desarrollo hardware, se realiza el diseño de esquemáticos y rutado de placas así como su fabricación y soldadura. Por tratarse de un sistema con procesado digital mediante FPGA, el desarrollo software cobra gran importancia y requiere conocimientos de modelado en lenguaje hardware VHDL así como programación en lenguaje C. Para ello se utiliza el kit de desarrollo de Xilinx modelo Virtex-5 ML507 que se presenta en detalle en el capítulo 5.

El uso de este kit requiere también aprender a manejar el software de desarrollo asociado, el "Embedded Design Kit" (EDK). Se trata de una plataforma de desarrollo de sistemas embebidos muy potente que contiene dos programas. El primero, llamado "Xilinx Platform Studio" (XPS), permite programar la FPGA mediante los "Intelectual Property Cores" (IPCores) que son bloques de código de descripción hardware o VHDL. En segundo lugar se dispone de la herramienta de

desarrollo software llamada "Software Development Kit" (SDK), desde donde se programa el procesador embebido en la FPGA.

#### 2.1 Entorno de trabajo

Parte de las herramientas software utilizadas en este proyecto requieren un sistema operativo específico para su correcto funcionamiento, concretamente el kit de desarrollo de Xilinx EDK en su versión 11.1, compatible con Windows XP. Se dispone de un portátil con Windows 7 como sistema operativo, por tanto, para solventar el inconveniente del EDK, se utiliza dicho portátil con una máquina virtual con Windows XP para asegurar la compatibilidad con todo el paquete de herramientas de Xilinx.

Tal como se ha dicho, este proyecto está orientado al uso de un sistema basado en FPGA con el uso del kit de evaluación de la tarjeta Virtex-5 ML507 de Xilinx, así como su entorno de desarrollo EDK con los programas XPS para el diseño hardware y SDK para diseño software de dicha tarjeta.

El diseño de la placa acondicionadora se realiza de forma manual, empleando el programa OrCAD. Para el diseño del esquemático del circuito se emplea OrCAD Capture, una vez finalizado el diseño del esquemático, se enlaza con la herramienta OrCAD Layout para proceder con el diseño del PCB.

Para que la presentación de resultados sea más visual por parte del usuario, se ha implementado una aplicación en LabVIEW mediante la que se controla la adquisición de datos y el modo de visualización y guardado de los mismos.

Para los cálculos de calibración del sistema se emplea el programa Excel, en el que se cargan los datos guardados previamente por la aplicación LabVIEW. Esta herramienta permite hacer cálculos de un modo rápido y sencillo, así como visualizar los resultados de forma gráfica para poder comprobar el correcto funcionamiento del sistema final.

Para la calibración final se utiliza un calibrador profesional marca FLUKE que permite simular temperaturas de termopar tipo J con una resolución de 0,1°C. Permite también generar un perfil de temperatura para comprobar la respuesta del sistema.

El calibrador se utiliza con el sistema completo, de este modo se pueden hacer las medidas necesarias, con las que posteriormente se realizan los cálculos de ajuste pertinentes para la calibración y posterior verificación del funcionamiento del sistema completo.

Las curvas de temperaturas medidas y cálculos necesarios para hallar los parámetros de calibración del sistema se realizan mediante hojas de cálculo de Excel.

## 3 Descripción del sensor de temperatura

#### 3.1 Introducción

Figura 3. Termopar tipo J.

La medida de temperatura ha sido muy empleada a lo largo de los años, desde los primeros termómetros de presión hasta los sensores más precisos de la actualidad. En muchos campos de ingeniería se necesita gran precisión en la medida de la temperatura, lo que ha provocado la aparición de muchos tipos de sensores diferentes.

Dependiendo de la finalidad del equipo, no es tan importante la sensibilidad del sensor como su robustez y su rango de temperaturas. Uno de los requisitos de este proyecto es el uso de termopares como sensor de medida de temperatura, este tipo de sensor se explica con más detalle en el apartado 3.4 de este capítulo. Dada su robustez, su sencillez de uso y su bajo coste, los termopares se emplean en muchos instrumentos de medida. Sin embargo, el comportamiento de los termopares puede suponer un problema para la estabilidad del sistema, debido a la falta de linealidad de su comportamiento, puesto que su respuesta tiene una desviación polinómica para las diferentes temperaturas dentro del rango de medida, al tratarse éste prototipo de un sistema con procesado digital, la no linealidad se puede compensar mediante aproximación por software, como se verá más adelante.

#### 3.2 Termoelectricidad

La termoelectricidad es la parte de la física termodinámica que explica las relaciones entre el flujo de calor y las corrientes eléctricas en un material. Esta parte de la ciencia da explicación a efectos como la generación de calor en la unión de dos conductores distintos cuando circula una corriente a través de ellos o el efecto contrario, es decir, la generación de una corriente eléctrica en un conductor cuando está sometido a un gradiente de temperatura. El estudio de estos y otros efectos eléctricos relacionados con la temperatura son, en su conjunto, lo que se hace llamar termoelectricidad.

#### 3.3 Termopares. El efecto Seebeck

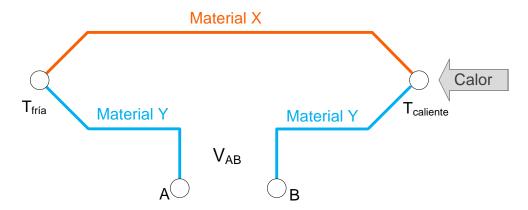

El primer efecto termoeléctrico descubierto fue el efecto Seebeck. El físico Thomas Johann Seebeck realizó experimentos en busca de una relación entre el calor y la electricidad. En 1921 descubrió que, soldando en lazo dos alambres de materiales diferentes (cobre y bismuto en su experimento) como en la figura 4, y aplicando calor a uno de ellos mientras el otro se mantenía frío, se generaba un campo magnético entre ambos, y si dicho calor era aplicado a la unión de los dos metales se generaba una corriente eléctrica a través de ellos.

Figura 4. Efecto Seebeck: Al aplicar calor a una unión de las uniones de dos materiales diferentes, se crea una diferencia de tensión proporcional a la temperatura aplicada.

Del modelo para el estudio del efecto Seebeck, visto en la figura 4, se extrae la relación entre la temperatura de ambas uniones y la tensión que se crea entre los bornes A y B, que se presenta en la ecuación 1:

$$V_{AB} = \alpha_{xy} \cdot (T_{caliente} - T_{fria}) \tag{Ec.1}$$

Ecuación 1. Del modelo del Efecto Seebeck se deduce la tensión diferencial proporcional a la temperatura de la unión caliente de dos hilos de materiales diferentes.

#### En la ecuación 1 se tiene:

- $V_{AB}$ : Tensión de salida en voltios (V)

- $\alpha$ : Coeficiente de Seebeck entre los dos materiales, x e y, expresado en voltios por grado Kelvin ( $V/^{\circ}K$ )

- T<sub>caliente</sub> T<sub>fria</sub>: Temperaturas caliente y fría de las uniones expresadas en grados Kelvin (°K)

De la ecuación 1 se obtiene la definición del Coeficiente Seebeck, que se expresa como la variación de la tensión en función de la temperatura:

$$\alpha_{xy} = \frac{\partial V_{AB}}{\partial T} \tag{Ec.2}$$

Ecuación 2. Definición del Coeficiente Seebeck, variación de la tensión en función de la temperatura aplicada.

Se deduce de la definición del efecto Seebeck, expresada en la ecuación 2, que no se puede medir directamente la tensión en bornes de los materiales ya que al conectar el voltímetro a éste, se crean dos nuevas uniones en el circuito. Estas dos nuevas uniones, generalmente de cobre, y la temperatura en su unión con los extremos del termopar hacen que varíe la tensión, por lo que se introduce un error en la medida realizada.

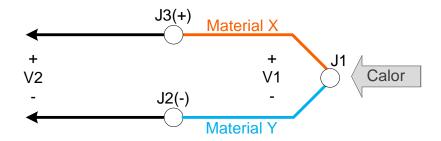

En la figura 5 se observa que debido a la conexión del termopar, la tensión a medir (V2), es función de la temperatura (V1) y de las tensiones parásitas debidas a las uniones J2 y J3. Por tanto es necesario conocer dichas tensiones parásitas, este efecto se conoce como "unión fría" y debe ser compensado para obtener una medida fiable.

Para ello, se debe saber la relación entre los materiales y la temperatura a la que están expuestos.

Figura 5. Unión fría creada al conectar un instrumento de media en los bornes del termopar, con ello se crean tensiones parásitas que deben ser compensadas.

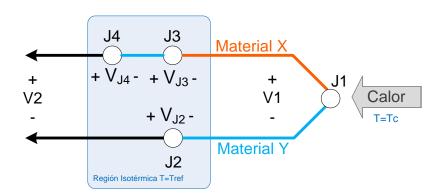

Un modo de conocer las tensiones parásitas es la inserción de un cable intermedio en una de las uniones, este cable debe ser del mismo material que el del hilo contrario, estas nuevas uniones deben estar contenidas en un ambiente isotérmico de temperatura conocida, tal como se muestra en la figura 6.

Figura 6. Modelo de compensación de la unión fría mediante región isotérmica. Se crean dos nuevas uniones de las mismas características (J2 y J4) de este modo se anulan las tensiones parásitas ( $V_{J2}$  y  $V_{J4}$ ). La compensación de la tensión parásita  $V_{J3}$  se debe hacer mediante software o hardware.

Se puede observar que las uniones J2 y J4 son del mismo material, por lo que tendrán el mismo comportamiento frente a la temperatura de la unión J1 lo que hace que sus tensiones parásitas ( $V_{J2}$  y  $V_{J4}$ ) se anulen. Por otro lado, la unión J3 tiene las mismas características que la unión J1, pero se encuentran a temperaturas diferentes. De esta manera se obtiene la siguiente relación:

$$V_2 = V_1(T_C) + V_{J3}(T_{ref})$$

(Ec.3)

Ecuación 3 Tensión resultante de la compensación de unión fría mediante región isotérmica.

La compensación de la tensión parásita  $V_{J3}$  se realiza mediante hardware o software dependiendo del tipo de diseño. La compensación hardware se realiza mediante una fuente de tensión contraria a la tensión  $V_{J3}$  de modo que ésta queda anulada y no afecta a la salida, la corrección hardware resulta costosa tanto en diseño como en materiales, por lo que en la actualidad se emplea muy poco. La compensación software requiere un procesador y un sensor de temperatura. Se procede midiendo la temperatura de la región isotérmica, que es la temperatura a la que está expuesta la unión J3; el procesador se encarga de hacer el cálculo de la tensión parásita y de restarlo a la salida, de modo que el valor de salida corresponde a la tensión resultante de la temperatura aplicada a la unión caliente. La compensación software tiene un diseño mucho más sencillo y menos costoso, resultando más fiable y más fácil de calibrar en caso de que se detecten desviaciones en la medida realizada.

#### 3.4 Tipos de Termopares

El efecto Seebeck se ha utilizado para la fabricación de sensores de temperatura (también llamados termopares). Tal como se ha detallado en el apartado anterior, manteniendo una de las dos soldaduras entre los dos materiales a una temperatura controlada y relativamente fría y utilizando el otro punto de unión de los materiales como detector de la temperatura de interés, se crea una diferencia de potencial V2, vista en la figura 7, directamente relacionada con la diferencia de temperatura entre las uniones de los dos materiales.

El termopar es el sensor de temperatura más utilizado comercialmente ya que se puede emplear para medir amplios intervalos de temperatura, son muy robustos, tienen una buena exactitud (si no se requiere la medida de variaciones muy pequeñas de temperatura), una rápida respuesta y un bajo coste.

Existen varios modelos de termopares dependiendo de los materiales que componen sus uniones como pueden ser: Cromo-Aluminio, Cromo-Constantan, Hierro-Constantan, Platino-Rodio, etc. A continuación se hace una breve descripción de los tipos más comunes, donde se detalla el rango de temperaturas y la sensibilidad media de cada tipo.

- Tipo K (Cromo (Ni-Cr) Chromel / Aluminio (aleación de Ni -Al) Alumel): con una amplia variedad de aplicaciones, está disponible a un bajo costo y en una variedad de sondas. Tienen un rango de temperatura de -200°C a +1.372°C y una sensibilidad media de 41μV/°C aproximadamente. Posee buena resistencia a la oxidación.

- Tipo E (Cromo / Constantan (aleación de Cu-Ni)): tienen una sensibilidad superior a los demás tipos, gracias a ello, son ideales para el uso en bajas temperaturas, en el ámbito criogénico. Tienen una sensibilidad media de 68μV/°C.

- Tipo J (Hierro / Constantan): debido a su limitado rango, el tipo J es menos popular que el K. El tipo J no puede usarse a temperaturas superiores a 760°C ya que una abrupta transformación magnética causa una descalibración permanente. Tienen un rango de -40°C a +750°C y una sensibilidad media de 52μV/°C. Es afectado por la corrosión.

- Tipo N (Nicrosil (Ni-Cr-Si / Nisil (Ni-Si)): es adecuado para mediciones de alta temperatura gracias a su elevada estabilidad y resistencia a la oxidación de altas temperaturas, y no necesita del platino utilizado en los tipos B, R y S que son más caros.

Por otro lado, los termopares tipo B, R y S son los más estables, pero debido a su baja sensibilidad media de unos  $10\mu V/^{\circ}C$ , generalmente son usados para medir altas temperaturas (por encima de los  $1000^{\circ}C$ ).

- Tipo B (Platino (Pt)-Rodio (Rh)): son adecuados para la medición de altas temperaturas superiores a 1.800°C. El tipo B por lo general presentan el mismo resultado a 0°C y 42°C debido a su curva de comportamiento.

- Tipo R (Platino (Pt)-Rodio (Rh)): adecuados para la medición de temperaturas de hasta 1.300°C. Su baja sensibilidad media (10μV/°C) y su elevado precio hacen que sea menos utilizado que otros tipos.

- Tipo S (Platino / Rodio): ideales para mediciones de altas temperaturas hasta los  $1.300^{\circ}$ C, pero su baja sensibilidad ( $10\mu V/^{\circ}$ C) y su elevado precio lo

convierten en un instrumento no adecuado para el uso general. Debido a su elevada estabilidad, el tipo S es utilizado para la calibración universal del punto de fusión del oro (1064,43°C).

En la tabla 1 se puede observar una clasificación de los tipos de termopar más comunes, incluyendo el material de sus uniones, así como el código de colores por el que se diferencian y el rango máximo de temperatura en el que se emplean.

| Código | Combinación de la aleación                   |                                              | Código de color |            | Rango Máximo de Temperatura |             |

|--------|----------------------------------------------|----------------------------------------------|-----------------|------------|-----------------------------|-------------|

| ANSI   | +                                            | -                                            | Termopar        | Extensión  | Termopar                    | Extensión   |

| E      | Cromel<br>Níquel-Cromo<br>Ni-Cr              | Constantan<br>Cobre-Níquel<br>Cu-Ni          | 1               | 1          | -270 a 1000°C               | 0 a 200°C   |

| 1      | Hierro<br>Fe                                 | Constantan<br>Cobre-Níquel<br>Cu-Ni          | 6               | <u> </u>   | -40 a 750°C                 | 0 a 200°C   |

| т      | Cobre<br>Cu                                  | Constantan<br>Cobre-Níquel<br>Cu-Ni          | 1               | <b>S</b> : | -270 a 400°C                | -60 a 100°C |

| К      | Cromel<br>Níquel-Cromo<br>Ni-Cr              | Alumel<br>Níquel-Aluminio<br>Ni-Al           | <b>E</b>        | 1          | -270 a 1372°C               | 0 a 200°C   |

| N      | Nicrosil<br>Níquel-Cromo-Silicio<br>Ni-Cr-Si | Nisil<br>Níquel-Silicio-Magnesio<br>Ni-Si-Mg |                 | 1          | -270 a 1300°C               | 0 a 200°C   |

| R      | Platino-13%Rodio<br>Pr-13%Rh                 | Platino<br>Pt                                | No establecido  | <u> </u>   | -60 a 1768°C                | 0 a 150°C   |

| s      | Platino-10%Rodio<br>Pr-10%Rh                 | Platino<br>Pt                                | No establecido  |            | -60 a 1768°C                | 0 a 150°C   |

| В      | Platino-30%Rodio<br>Pr-30%Rh                 | Platino-6%Rodio<br>Pr-6%Rh                   | No establecido  | -          | 0 a 1820°C                  | 0 a 100°C   |

Tabla 1. Comparativa de los tipos de de termopares más comunes según material y rango de temperatura.

Como se puede ver en la figura 7, para los diferentes tipos de termopar existen diferentes gráficos de comportamiento. Se puede observar que a partir de 100°C la linealidad prácticamente se conserva. A temperaturas más bajas la aproximación de las medidas respecto a la temperatura real es polinómica.

Figura 7. Tensión de termopar frente a temperatura según los diferentes tipos de termopares.

La mayoría de controladores de temperatura comerciales utilizan la compensación por software para realizar la medición de temperatura en un dispositivo termopar. Así mismo, también realizan los cálculos necesarios para corregir la no linealidad de estos dispositivos a bajas temperaturas.

#### 3.5 Sensor Utilizado: Tipo J

Uno de los requisitos de este proyecto es el empleo de termopares tipo J. Tal como se ha observado en la tabla 1, este tipo de termopar cubre el rango de temperaturas que se pretende medir, que será de 0 a  $200^{\circ}$ C. Tiene una sensibilidad media de unos  $52\mu V/^{\circ}$ C.

A la hora de calibrar el sistema, se deberá tener en cuenta que esta sensibilidad no es lineal en todo el rango de medida sino que varía según la temperatura que se esté midiendo, existen unos coeficientes para el cálculo de calibración, como se puede ver en la tabla 2, estos coeficientes se aplican tal como se indica en la ecuación 4:

$$E_{0j} = b_0 + b_1 T_j + b_2 T_{2j} + \dots + b_n T_{nj}$$

; donde  $T_j$  en  ${}^{\circ}C y E_{0j}$  en  $mV$ . (Ec. 4)

Ecuación 4. Calibración de termopar tipo J por coeficientes en función de la temperatura.

|       |   | $-210^{\circ}C \le T \le 760^{\circ}C$   | $760^{\circ}C \le T \le 1200^{\circ}C$ |

|-------|---|------------------------------------------|----------------------------------------|

| $b_0$ | = | 0                                        | 2,9645625681 10 <sup>2</sup>           |

| $b_1$ | = | 5,0381187185 10-2                        | -1,4976127790                          |

| $b_2$ | = | 3,0475386930 10-5                        | 3,1787103294 10 <sup>-3</sup>          |

| $b_3$ | = | -8,5681065720 10 <sup>-8</sup>           | -3,1847686701 10-6                     |

| $b_4$ | = | 1,3228195295 10-10                       | 1,5720819004 10 <sup>-9</sup>          |

| $b_5$ | = | <i>-</i> 1,7052958337 10 <sup>-</sup> 13 | -3,0691369056 10 <sup>-13</sup>        |

| $b_6$ | = | 2,0948090690 10-16                       | 0                                      |

| $b_7$ | = | -1,2538395226 10 <sup>-19</sup>          | 0                                      |

| $b_8$ | = | 1,5631725697 10-23                       | 0                                      |

Tabla 2. Coeficientes para la calibración de termopar tipo J en función del rango de temperatura.

El conversor de termopar a trama digital que se utiliza en este proyecto, realiza tanto la compensación de la unión fría como la calibración de las temperaturas. El conversor transforma dichas medidas en su valor decimal en °C correspondiente. Se debe tener en cuenta tanto el tipo de calibración que realiza el conversor, como el resultado de la compensación interna de la unión fría. Estos puntos se estudian a lo largo de esta memoria, se podrá comprobar que el conversor asume un comportamiento lineal en los termopares, y que para mejorar la compensación de la unión fría, el chip se deberá colocar lo más cerca posible del conector de termopar y en un ambiente lo más estable posible, evitando corrientes de aire.

# 4 Descripción del conversor

# 4.1 Introducción

Figura 8. Encapsulado MAX31855.

Para convertir la tensión generada en el termopar a un valor digital correspondiente a la temperatura medida, en rasgos generales se deberá emplear un amplificador operacional, puesto que el rango de tensiones del termopar es muy pequeño, también sería necesario el uso de un conversor analógico digital o ADC (Analog to Digital Converter), así como un sensor de temperatura para poder hacer la compensación de la unión fría tal como se explica en el apartado anterior.

Los avances en miniaturización y el crecimiento en la oferta de componentes que integran varias funcionalidades en un solo chip, nos permiten encontrar elementos como el que se utiliza en este proyecto. Se trata de un conversor de termopar a digital que incluye compensación de la unión fría.

A continuación se detallan los aspectos más importantes a tener en cuenta en el diseño de la placa acondicionadora y al mismo tiempo se describe el conversor empleado, incluyendo la información más relevante de la hoja de especificaciones facilitada por el fabricante.

# 4.2 Conversor de Termopar a Digital con Compensación de la Unión Fría

Para la conversión de termopar a digital se utiliza el "Cold-Junction Compensated Thermocouple-to-Digital Converter" (en español: Conversor de Termopar a Digital con Compensación de Unión Fría) cuya referencia es MAX31855 del fabricante Maxim, concretamente se trata del MAX31855JASA+ que es el correspondiente al termopar tipo J.

#### 4.2.1 Descripción Hardware

Este componente reune los elementos necesarios para hacer la conversión de termopar a digital ya comentados en el apartado 4.1 de este capítulo. En la figura 9 se puede observar la composición interna del mismo, que consta de una entrada para termopar que se chequea para conocer el estado de la conexión, seguida de un amplificador operacional. Dispone de un bloque especial dedicado a la compensación de la unión fría, que incluye un sensor que realiza la medición de la temperatura ambiente y le aplica la sensibilidad del termopar utilizado, por esta razón es importante tener en cuenta que el tipo de termopar deben coincidir con el encapsulado del MAX utilizado. La salida del amplificador ya compensada es enviada a un ADC con control digital, quedando a la salida del MAX las tres señales digitales que forma la comunicación SPI, éstas son SCK que es el reloj que sincroniza la comunicación, SO es la salida de datos digital por donde se enviará la trama hacia la FPGA, y /CS es la señal de entrada de selección que se activará desde la FPGA.

Figura 9. Diagrama de bloques. MAX31855, incluye un amplificador operacional, detección del estado de la conexión del termopar y un bloque especial para la compensación de la unión fría, así como un ADC para hacer la conversión de termopar adigital

En la figura 10 se puede ver el circuito típico de conexión del MAX31855 recomendado por el fabricante, donde se especifica la entrada del termopar indicando el positivo y el negativo. Se observa también, a modo de ejemplo, la conexión de la salida hacia un microcontrolador, pero en este proyecto el procesado digital se realiza mediante el procesador PowerPC de la tarjeta Virtex-5.

Figura 10. Circuito de aplicación típico del MAX31855, a la entrada se conecta el termopar, la comunicación SPI se gestionará en este caso con el procesador de la FPGA.

Las condiciones de trabajo recomendadas por el fabricante se resumen en la tabla 3. La tensión de alimentación típica es de 3,3V que es un valor común en la alimentación de circuitos digitales, esta alimentación se podrá obtener de la FPGA ya que dispone de pines de salida de alimentación a 3,3V. Se debe tener en cuenta también que se respeta el rango de tensión de los niveles lógicos,  $V_{\rm IL}$  para nivel bajo y  $V_{\rm IH}$  para el nivel alto.

#### PARÁMETROS DE FUNCIONAMIENTO

(TA = -40°C to +125°C, unless otherwise noted.)

| PARAMETER            | SYMBOL          | CONDITIONS | MIN  | TYP | MAX                   | UNITS |

|----------------------|-----------------|------------|------|-----|-----------------------|-------|

| Power-Supply Voltage | V <sub>CC</sub> | (Note 2)   | 3.0  | 3.3 | 3.6                   | V     |

| Input Logic 0        | VIL             |            | -0.3 |     | +0.8                  | ٧     |

| Input Logic 1        | V <sub>IH</sub> |            | 2.1  |     | V <sub>CC</sub> + 0.3 | V     |

Tabla 3. Condiciones de trabajo del MAX31855 recomendados por el fabricante.

En la tabla 4 se pueden ver las características térmicas del MAX31855 en su uso con termopares tipo J, de la primera fila de esta tabla se deduce que el conversor asume una sensibilidad del termopar constante, con un valor de  $57,953\mu\text{V}/^{\circ}\text{C}$ , por lo que la compensación no tendrá en cuenta la no linealidad en la medida del termopar.

Se puede observar también la resolución de la conversión de temperatura del termopar, que es de 0,25°C, y la resolución de la temperatura medida en la unión fría, que es de 0,0625°C. Es importante tener en cuenta estos valores a la hora de procesar las medidas en el procesador de la FPGA

#### CARACTERÍSTICAS TÉRMICAS

| $(3.0V \le V_{CC} \le 3.6V)$ | $T_A = -40^{\circ}C \text{ to } + 125^{\circ}C,$ | unless otherwise noted.) | (Note 4) |

|------------------------------|--------------------------------------------------|--------------------------|----------|

|------------------------------|--------------------------------------------------|--------------------------|----------|

| PARAMETER                                                                        | SYMBOL   | CONDITIONS                                                                                                                                          | MIN | TYP    | MAX | UNITS |

|----------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-----|-------|

| MAX31855J Thermocouple<br>Temperature Gain and Offset                            |          | $T_{\text{THERMOCOUPLE}} = -210^{\circ}\text{C to } +750^{\circ}\text{C},$<br>$T_{\text{A}} = -20^{\circ}\text{C to } +85^{\circ}\text{C (Note 3)}$ | -2  |        | +2  | °C    |

| Error (57.953µV/°C nominal sensitivity) (Note 4)                                 |          | Thermocouple = $-210^{\circ}$ C to $+1200^{\circ}$ C,<br>T <sub>A</sub> = $-40^{\circ}$ C to $+125^{\circ}$ C (Note 3)                              | -4  |        | +4  |       |

| Thermocouple Temperature Data Resolution                                         |          |                                                                                                                                                     |     | 0.25   |     | °C    |

| Internal Cold-Junction                                                           |          | $T_A = -20^{\circ}\text{C to } +85^{\circ}\text{C (Note 3)}$                                                                                        | -2  |        | +2  | °C    |

| Temperature Error                                                                |          | $T_A = -40^{\circ}\text{C to } + 125^{\circ}\text{C (Note 3)}$                                                                                      | -3  |        | +3  |       |

| Cold-Junction Temperature Data<br>Resolution                                     |          | $T_A = -40^{\circ}\text{C to } + 125^{\circ}\text{C}$                                                                                               |     | 0.0625 |     | °C    |

| Temperature Conversion Time<br>(Thermocouple, Cold Junction,<br>Fault Detection) | tCONV    | (Note 5)                                                                                                                                            |     | 70     | 100 | ms    |

| Thermocouple Conversion<br>Power-Up Time                                         | tCONV_PU | (Note 6)                                                                                                                                            | 200 |        |     | ms    |

Tabla 4. Características térmicas y tiempos de conversión del MAX31855 en su versión para termopar tipo J.

El error introducido por el conversor para la temperatura del termopar es de ±2°C, en el rango de temperaturas de -210°C a 750°C, que es el rango en el que trabajará el prototipo. Para unas condiciones de trabajo con temperatura ambiente entre -20°C y 85°C, el error introducido en la medida de la temperatura de la unión fría puede llegar también a los ±2°C.

Tanto el error introducido por el conversor, como el error en la conversión debido a la no linealidad de la medida real del termopar, deberán ser minimizados mediante calibración software.

Puesto que la aplicación del prototipo no requiere una velocidad de transmisión muy elevada, los tiempos de conversión se respetarán sin problemas ya que el tiempo entre medidas será mucho mayor de 100ms. El tiempo de inicialización también se respetará, puesto que la inicialización del resto de elementos del sistema es mayor que el tiempo de inicialización del MAX31855 de 200ms.

En la figura 11 se encuentra la descripción de pines del MAX31855, así como su disposición en el encapsulado de ocho pines de montaje superficial tipo SOP, que es el encapsulado utilizado en este diseño.

#### **PINOUT**

| PIN | NAME            | FUNCTION                                                                               |

|-----|-----------------|----------------------------------------------------------------------------------------|

| 1   | GND             | Ground                                                                                 |

| 2   | T-              | Thermocouple Input. See Table 1. Do not connect to GND.                                |

| 3   | T+              | Thermocouple Input. See Table 1.                                                       |

| 4   | V <sub>CC</sub> | Power-Supply Voltage                                                                   |

| 5   | SCK             | Serial-Clock Input                                                                     |

| 6   | CS              | Active-Low Chip Select. Set $\overline{\text{CS}}$ low to enable the serial interface. |

| 7   | SO              | Serial-Data Output                                                                     |

| 8   | DNC             | Do Not Connect                                                                         |

Figura 11. Pinout del MAX31855. Encapsulado tipo SOP de 8 pines.

#### 4.2.2 Descripción Software

En toda comunicación digital es necesario conocer la configuración de la señal, En la figura 12 y 13 se muestran los diagramas del protocolo y los tiempos a tener en cuenta en la comunicación serie del sistema entre el bloque de conversión y el de procesado digital, de estas imagenes se obtiene la información del flanco activo de reloj, de subida en este caso, así como el orden de envío de los bits de datos. En el diagrama del protocolo se observa que el bit de menor peso D0 es el primero que se envía, por lo que se sabe que en recepción, en la FPGA, el primer bit recibido será el menos significativo o LSB. En el diagrama de tiempos aparecen indicados los tiempos mínimos que se deben respetar para que la comunicación se realice de forma correcta. Estos tiempos se detallan en la tabla 5, de donde se obtiene la información necesaria para configurar la comunicación desde la FPGA, en esta tabla, el fabricante indica que la frecuencia de reloj deberá ser como máximo de 5MHz.

#### PROTOCOLO DE INTERFAZ SERIE

Figura 12. Diagrama del protocolo de la comunicación SPI.

#### TEMPORIZACIÓN DE INTERFAZ SERIE

Figura 13. Diagrama de tiempos de la comunicación SPI.

#### CARACTERÍSTICAS DE TIEMPOS COMUNICACIÓN SPI

| PARAMETER                     | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------|-----------------|------------|-----|-----|-----|-------|

| Input Leakage Current         | ILEAK           | (Note 7)   | -1  |     | +1  | μА    |

| Input Capacitance             | C <sub>IN</sub> |            |     | 8   |     | pF    |

| Serial-Clock Frequency        | fscL            |            |     |     | 5   | MHz   |

| SCK Pulse-High Width          | tcH             |            | 100 |     |     | ns    |

| SCK Pulse-Low Width           | t <sub>CL</sub> |            | 100 |     |     | ns    |

| SCK Rise and Fall Time        |                 |            |     |     | 200 | ns    |

| CS Fall to SCK Rise           | tcss            |            | 100 |     |     | ns    |

| SCK to CS Hold                |                 |            | 100 |     |     | ns    |

| CS Fall to Output Enable      | t <sub>DV</sub> |            |     |     | 100 | ns    |

| CS Rise to Output Disable     | t <sub>TR</sub> |            |     |     | 40  | ns    |

| SCK Fall to Output Data Valid | t <sub>DO</sub> |            |     |     | 40  | ns    |

| CS Inactive Time              |                 | (Note 3)   | 200 |     |     | ns    |

Tabla 5. Características de los tiempos en la comunicación SPI.

En el diagrama de la figura 12 se ha observado el protocolo de la trama de comunicación SPI. La descripción del contenido de esta trama aparece en la tabla 6, Los tres bits de menor peso D0, D1, D2 informan sobre el estado de la conexión del termopar, si está cortocircuitado a masa, a alimentación o si no está conectado. Los siguiente doce bits D[15..4] contienen el valor de la temperatura medida en la unión fría, con el bit D16 se puede chequear si cualquiera de los tres bits más bajos está activado, es decir, si hay algún fallo en la conexión del termopar. Los catorce bits de mayor peso D[31..18] contienen el valor correspondiente a la medida del termopar, con una resolución de 0,25°C, como se ha explicado en las características generales del conversor.

#### MAPA DE MEMORIA

| BIT      | NAME                                    | DESCRIPTION                                                                                            |

|----------|-----------------------------------------|--------------------------------------------------------------------------------------------------------|

| D[31:18] | 14-Bit Thermocouple<br>Temperature Data | These bits contain the signed 14-bit thermocouple temperature value. See <u>Table 4</u> .              |

| D17      | Reserved                                | This bit always reads 0.                                                                               |

| D16      | Fault                                   | This bit reads at 1 when any of the SCV, SCG, or OC faults are active. Default value is 0.             |

| D[15:4]  | 12-Bit Internal Temperature<br>Data     | These bits contain the signed 12-bit value of the reference junction temperature. See <u>Table 5</u> . |

| D3       | Reserved                                | This bit always reads 0.                                                                               |

| D2       | SCV Fault                               | This bit is a 1 when the thermocouple is short-circuited to V <sub>CC</sub> . Default value is 0.      |

| D1       | SCG Fault                               | This bit is a 1 when the thermocouple is short-circuited to GND. Default value is 0.                   |

| D0       | OC Fault                                | This bit is a 1 when the thermocouple is open (no connections). Default value is 0.                    |

Tabla 6. Descripción del Mapa de Memoria. Indica la posición de los bits y la información de la trama.

Para poder procesar las temperaturas contenidas en la trama serie, es necesario conocer el formato de los datos. Esta información se encuentra detallada en los ejemplos de la tabla 7. A la izquierda se encuentran ejemplos con el formato de la trama, en binario, correspondiente al valor de temperatura del termopar y a la derecha, el correspondiente a la temperatura de la unión fría. Como ya se indicaba en la tabla 4, la resolución del termopar es de 0.25°C, las dos cifras decimales vienen dadas por los dos últimos bits, sin embargo, para la temperatura de la unión, la resolución de 0,625°C y estos tres decimales vendrán dados por los cuatro últimos bits.

Es importante estudiar estas tablas con detalle para encontrar el mejor modo de procesar la información una vez que se reciba en la FPGA para su posterior calibración.

#### TEMPERATURA TERMOPAR

| TEMPERATURE<br>(°C) | DIGITAL OUTPUT<br>(D[31:18]) |

|---------------------|------------------------------|

| +1600.00            | 0110 0100 0000 00            |

| +1000.00            | 0011 1110 1000 00            |

| +100.75             | 0000 0110 0100 11            |

| +25.00              | 0000 0001 1001 00            |

| 0.00                | 0000 0000 0000 00            |

| -0.25               | 1111 1111 1111 11            |

| -1.00               | 1111 1111 1111 00            |

| -250.00             | 1111 0000 0110 00            |

#### TEMPERATURA UNIÓN FRÍA

| TEMPERATURE<br>(°C) | DIGITAL OUTPUT<br>(D[15:4]) |

|---------------------|-----------------------------|

| +127.0000           | 0111 1111 0000              |

| +100.5625           | 0110 0100 1001              |

| +25.0000            | 0001 1001 0000              |

| 0.0000              | 0000 0000 0000              |

| -0.0625             | 1111 1111 1111              |

| -1.0000             | 1111 1111 0000              |

| -20.0000            | 1110 1100 0000              |

| -55.0000            | 1100 1001 0000              |

Tabla 7. Formato de la temperatura en la trama de comunicación serie. Izquierda: temperatura del termopar, derecha: Temperatura de la unión fría.

# 5 Sistema de control y procesado: FPGA

### 5.1 Introducción

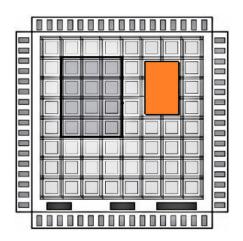

Figura 14. Vista simplificada de una FPGA.

Εl de FPGAs en uso diseños electrónicos está cada vez más extendido debido en parte a la bajada de precios y a los avances en las técnicas de fabricación de placas electrónicas. Las FPGAs resultan idóneas para prototipado por la gran flexibilidad que tienen en cuanto a diseño, así como la facilidad de reprogramación, lo que supone una gran ventaja a la hora de hacer pruebas en un sistema. En la actualidad hay modelos que incorporan un procesador embebido, representado en naranja en la figura 14, de modo que la eficiencia y

velocidad de procesado aumenta respecto a los modelos en los que el procesador es simulado mediante la lógica interna de la FPGA.

El sistema de control de comunicaciones y procesado de señales de este proyecto se implementa mediante el kit de desarrollo de Xilinx modelo Virtex-5 FXT ML507 basado en la FPGA modelo *XC5VFX70T-2FFG1136C*, la cual tiene embebido un procesador PowerPC440. En este capítulo se presentan las nociones básicas de FPGAs y las herramientas proporcionadas por el fabricante para el desarrollo de los sistemas embebidos.

## **5.2 FPGA**

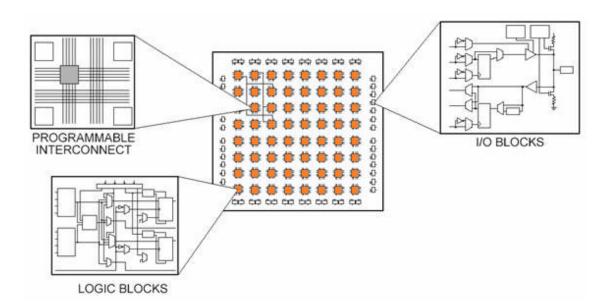

Una FPGA (Field Programmable Gate Array) es un dispositivo semiconductor formado por un conjunto de bloques lógicos programables y recursos de interconexión también programables. Los bloques lógicos pueden ser programados para duplicar la funcionalidad de puertas lógicas, tales como AND, OR, XOR, NOT o funciones combinacionales más complejas, tales como decodificadores o simples funciones matemáticas. En muchas FPGA, estos componentes lógicos programables también incluyen elementos de memoria, los cuales pueden ser simples flip-flops o bloques de memoria más complejos. El código se programa directamente en el hardware, de modo que éste puede adoptar casi cualquier arquitectura. Las herramientas de síntesis determinan la forma de configurar todos los elementos que componen la FPGA para que el funcionamiento sea el descrito por el programador. En la figura 15 se puede ver de forma esquemática la arquitectura de una FPGA, en naranja se representan los bloques lógicos, y en los cuatro extremos los bloques de entrada salida (bloques I/O), dichos bloques están interconectados por una red reconfigurable de pistas.

Los últimos avances en esta tecnología se centran en conseguir un "Sistema programable en un único chip", para ello se combinan los bloques lógicos e interconexiones tradicionales de las FPGAs, con microporcesadores y periféricos relacionados. La tendencia es embeber éstos en el chip de la FPGA de modo que se combinan los soft-cores (bloques lógicos e interconexiones) con hard-cores, es decir el chip de silicio que compone el procesador embebido, tal como se ha visto en la figura 14, representado en color naranja.

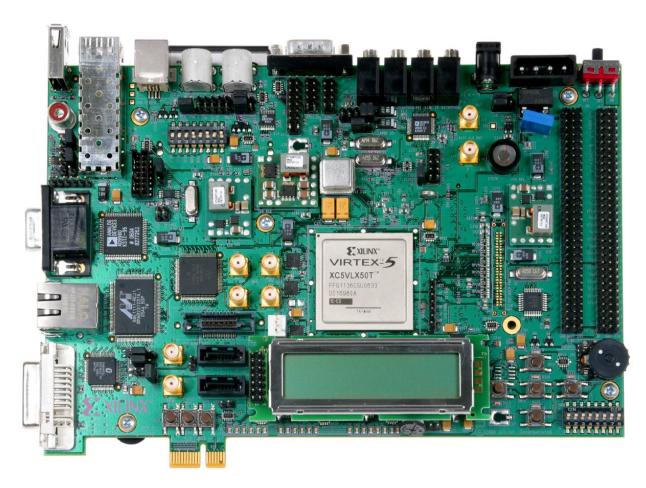

# 5.3 Kit de desarrollo

Como ya se ha comentado, este proyecto se basa en la FPGA Virtex-5 modelo XC5VFX70T-2FFG1136C de Xilinx, ésta FPGA contiene un procesador PowerPC440 embebido. El kit de evaluación que se utiliza para el procesado digital y control de comunicaciones del prototipo es el Virtex-5 ML507 que se muestra en la figura 16, incluye una gran diversidad de periféricos a disposición del diseñador. Cada periférico deberá ir asociado a un código diseñado en lenguaje de descripción hardware (VHDL), dichos bloques son los llamados IPCore (Bloque de Propiedad Intelectual). Contienen parte de la información necesaria para la configuración interna de la FPGA, para completar el diseño se deben describir, también en lenguaje de descripción hardware, las restricciones que tiene el diseño, como por ejemplo señales de reloj, señales que requieren un retardo específico, y demás elementos críticos. Estos programas se implementan en la FPGA por medio de sus herramientas de desarrollo asociadas.

Figura 16. Placa de desarrollo Virtex-5 ML507.

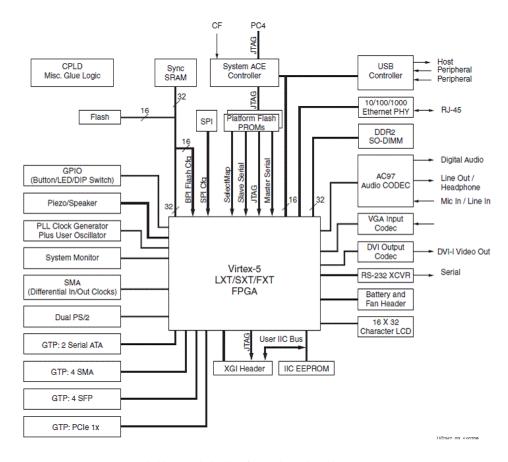

# 5.4 Diagrama de bloques

La placa de desarrollo Virtex-5 FXT ML507 contiene, como ya se ha visto, el modelo de FPGA XC5VFX70T-2FFG1136C del fabricante Xilinx. Además de numerosos periféricos disponibles para su uso mediante la configuración de la FPGA, como pueden ser entradas de audio, vídeo, USB, memorias, pulsadores, LEDs, pines de entrada salida de propósito general (GPIO), etc. A continuación se describen los elementos utilizados en el diseño.

- **Microprocesador:** Es un PowerPc 440 embebido en la *FPGA* en forma de bloque y que se configura mediante las herramientas de Xilinx.

- Comunicaciones externas: Se refiere a todos los elementos que permiten la comunicación de la tarjeta con otro dispositivo externo.

- **Serie:** Para la comunicación serie se utiliza un IPCore que implementa una UART en la FPGA.

- **SPI:** Utilizado para controlar la comunicación SPI si se configura como maestro.

- **JTAG:** La conexión JTAG permite configurar la PROM donde se almacena la configuración de la FPGA y depurar el PowerPc 440.

- **Memorias:** El bloque de memorias está formado por tres tipos de memorias:

- **DRAM**: Se dispone de 512Mbyte de memoria DDR2 SDRAM de 333MHz, distribuida en dos módulos de 256 Mbytes (modelo MT47H128M16HG-3 IT de Micron).

- Flash: Se dispone 128 Mbyte de memoria de tipo NOR (modelo PC28F00AP30TF de Numonyx).

- **PROM**: Tiene 32 Mbyte y es el modelo XCF32P de Xilinx.

- Entrada salida de propósito general (GPIO): Agrupa diferentes elementos de entrada/salida de propósito general:

- **LEDs:** Se dispone de ocho diodos LED.

- Conector de expansión: El conector J6 de la placa, se puede configurar tanto en modo diferencial como single. Se utiliza para la conexión de la comunicación SPI.

En el diagrama de bloques de la figura 17 aparecen representados los periféricos disponibles en la tarjeta Virtex-5 ML507 incluyendo los que se utilizan en este proyecto, descritos anteriormente.

Figura 17. Diagrama de bloques de la plataforma de evaluación FPGA Virtex-5 ML507.

Xilinx proporciona un entorno de desarrollo llamado Embedded Development Kit (EDK) formado por dos herramientas muy potentes, una es la plataforma destinada a la implementación hardware de la FPGA, llamada Xilinx Platform Studio (XPS), que incluye los IPCores facilitados por el fabricante, así como todo el entorno necesario para realizar la configuración de los dispositivos que se vayan a utilizar. Y la otra, el Software Development Kit (SDK) destinado a la programación del software para el procesador del sistema, ya sea simulado (Microblaze) o embebido (PowerPC). Este entorno se describe en más detalle en el capítulo 8

# 6 Arquitectura del sistema completo

# 6.1 Introducción

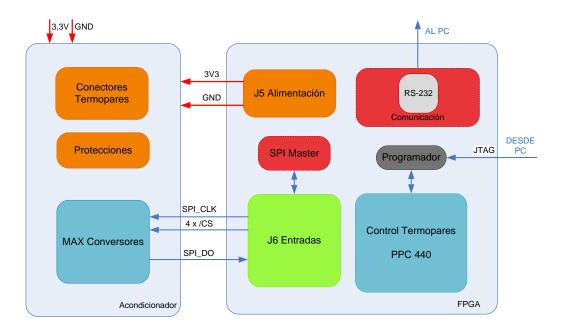

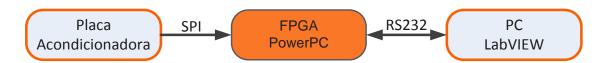

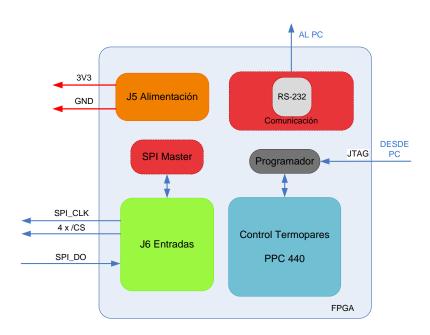

Figura 18. Diagrama de bloques global

En este capítulo se presentan los bloques que componen el sistema final para poder tener una primera aproximación del funcionamiento global. Se describen los tres bloques en los que se ha divido el mismo. Cada bloque atiende a la naturaleza de los elementos que lo componen, simplificando así su estudio y presentación. En primer lugar se tiene el sensor de temperatura y su conversión a digital para la posterior comunicación, dichos elementos componen el primer bloque, en este documento también se hace referencia a dicho bloque como "placa acondicionadora de señal". A continuación se tiene la gestión de las comunicaciones y el procesado de la temperatura medida, de esto se encarga la FPGA, en la que estará implementado el módulo de control de la comunicación SPI con la placa acondicionadora, el de comunicación serie con el PC así como el código para el procesado de temperaturas y gestión de comunicaciones. Por último, la parte de software, en el PC se implementa la interfaz de usuario y se realizan los cálculos de calibración. Todo el software de programación y configuración de la FPGA se realiza desde el PC tal como se explica en el capítulo 8.

En los capítulos anteriores se ha presentado el estudio realizado sobre el funcionamiento del sensor de temperatura, del conversor de termopar a digital y de la FPGA. En los siguientes capítulos se describen los diferentes bloques que se presentan en este capítulo, profundizando más en el diseño y el funcionamiento de cada bloque.

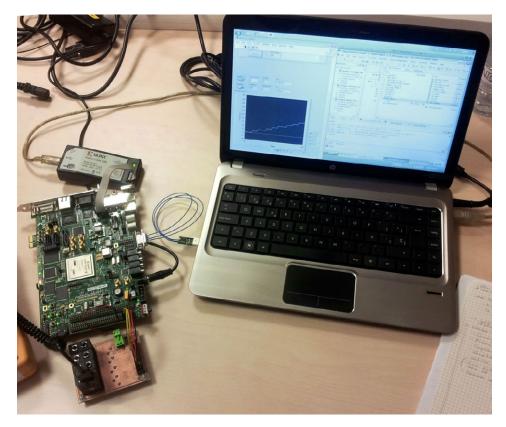

# 6.2 Visión general del sistema completo

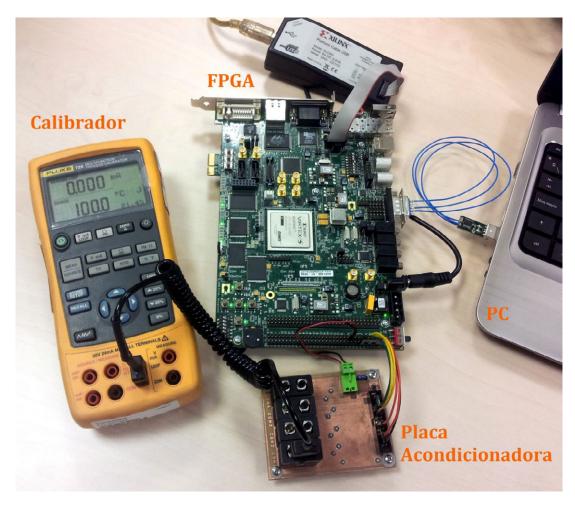

El sistema final, tal como se observa en la figura 19, está compuesto por los bloques descritos en el apartado anterior, figura 18, que son la placa acondicionadora que compone el bloque I, y que incluye el hardware necesario para la conversión analígico-digital. La FPGA tiene dos funciones principales, la primera es hacer de puente entre la placa y el PC, a su entrada controla la comunicación SPI con la placa acondicionadora y a su salida la comunicación serie con el PC, y la segunda es realizar la calibración y procesado de la trama SPI. Recibe la trama que contiene las medidas realizadas por el MAX31855, aplica la calibración a dichas medidas y conforma una nueva trama que envía por puerto serie al PC. El tercer y último bloque, a la derecha en la imagen, está formado por el PC con las aplicaciones necesarias para la programación de la FPGA con el paquete de desarrollo software EDK de Xilinx.

Figura 19. Sistema completo.

El diseño e implementación del primer bloque se presenta en más detalle en el capítulo 7 de esta memoria, se explica el proceso de diseño del esquemático y el posterior diseño de la placa acondicionadora así como el proceso de fabricación de la misma.